Engineering, 03.06.2021 02:00, pedrojsq271

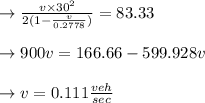

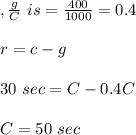

4 An approach to a pretimed signal has 30 seconds of effective red, and D/D/1 queuing holds. The total delay at the approach is 83.33 veh-s/cycle and the saturation flow rate is 1000 veh/h. If the capacity of the approach equals the number of arrivals per cycle, determine the approach flow rate and cycle length.

Answers: 3

Other questions on the subject: Engineering

Engineering, 04.07.2019 19:10, nbunny7208

What is the chief metrological difference between measuring with a microscope and with an electronic comparator? a. the microscope is limited to small workpieces. a. the microscope is limited to small workpieces. c. the comparator can only examine one point on the workpiece. d. the microscope carries its own standard.

Answers: 1

Engineering, 04.07.2019 19:20, lordcaos066

Determine the time of the day and month of the year at which the peak sensible cooling load occurs for a top floor, north-eastern corner room of an office building in durban for the following conditions: floor area: 8 x 8 x 3 m east and north walls: 115 mm face brick (outside), 20 mm air space, 115 mm ordinary brick (inside) with 15 mm plaster roof construction: suspended plasterboard ceiling, 450 mm air space, 150 mm concrete, 75mm screed, waterproofing no heat transfer across other surfaces window area 3x 1,5 m high in north wall only. ordinary glass with venetian blinds. lights and occupants : from 07: 00 to 18: 00 average light density: 25 w/m2 number of occupants : 5 seated, light office work room temperature 24°c

Answers: 3

Engineering, 06.07.2019 02:30, khalilh1206

1in2 processor chip can be modelled as an isothermal plane wall of silicon, isothermal on both sides. the power input to the bottom of the plane wall, or the processing power of the chip, often called the thermal design power (tdp), is 100w. assume the periphery is adiabatic. the silicon is 400 microns thick. the temperature at the junction, or in this case on the bottom of the isothermal plane wall, is 85°c. what is the top surface temperature, assuming that the only mode of heat transfer is conduction

Answers: 1

Do you know the correct answer?

4 An approach to a pretimed signal has 30 seconds of effective red, and D/D/1 queuing holds. The tot...

Questions in other subjects:

Mathematics, 26.10.2021 15:20

Arts, 26.10.2021 15:20